در قسمتهای قبل با سختافزار برد STM32H745I-DISCO آشنا شدیم و یک پروژه ساده Blinky را روی هر کدام از هستهها اجرا کردیم. حالا وقت آن است که با یکی از مهمترین قابلیتهای هسته Cortex-M7 یعنی سطح اول حافظه کش (L1 Cache) آشنا شویم.

قسمت سوم

برای دیدن قسمت دوم اینجا کلیک کنید.

ویدیو آموزشی STM32H7 |قسمت سوم: آشنایی با I-Cache و D-Cache در پردازندههای STM32H7

مقدمهای بر حافظه کش در STM32H7

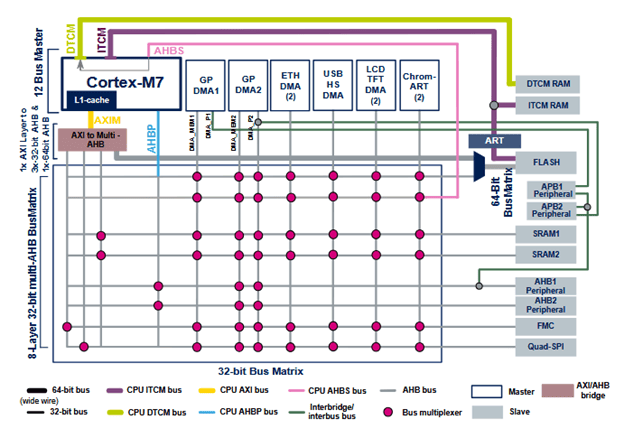

بلوک دیاگرام کش در stm32H7

پردازنده Cortex-M7 موجود در STM32H7 شامل دو نوع کش سطح اول (L1) است:

- Instruction Cache (I-Cache): برای ذخیره دستورالعملهای پراستفاده و جلوگیری از خواندن مکرر آنها از حافظههای کندتر مثل Flash یا حافظه خارجی.

- Data Cache (D-Cache): برای ذخیره دادههایی که زیاد استفاده میشوند، بهخصوص هنگام دسترسی به حافظههایی با تأخیر بالا.

هر دو کش در STM32H7 ظرفیت ۱۶ کیلوبایت دارند و به صورت زیر طراحی شدهاند:

- I-Cache: دو راهه (2-way set associative)

- D-Cache: چهار راهه (4-way set associative)

- طول هر خط کش: ۳۲ بایت

- دارای ECC برای حفاظت در برابر خطاهای حافظه کش

چرا کش مهم است؟

در معماری STM32H7، بسیاری از حافظهها مثل Flash داخلی، SDRAM خارجی، QSPI Flash از طریق AXI Bus به پردازنده متصلاند، این حافظهها معمولاً چند سیکل زمان نیاز دارند تا داده یا دستورالعمل را تحویل دهند. کش این فاصله را پنهان میکند و باعث افزایش سرعت اجرای کد و پردازش دادهها میشود.

مثال ساده: فرض کنید یک حلقه کوچک بارها اجرا میشود. بدون کش، پردازنده هر بار باید دستورالعملها را از حافظه Flash بخواند (کندتر). با کش، همان دستورات یک بار خوانده میشوند و در حافظه سریع کش ذخیره میگردند.

تفاوت I-Cache و D-Cache

| ویژگی | I-Cache | D-Cache |

|---|---|---|

| نوع داده | دستورالعملها (Code) | دادهها (Data) |

| هدف | کاهش تأخیر در واکشی کد | کاهش تأخیر در خواندن/نوشتن داده |

| حالت نوشتن | ندارد (فقط خواندن) | دارد: Write-Through یا Write-Back |

| مشکلات همزمانی (Coherency) | معمولاً کمتر | بیشتر (به دلیل حالت Write-Back) |

سیاستهای کش در STM32H7

حالتهای مهم در D-Cache:

- Write-Through (WT):

- هر تغییر بلافاصله به حافظه اصلی نوشته میشود.

- مزیت: همواره داده حافظه اصلی و کش یکسان است.

- عیب: نوشتنهای بیشتر روی باس → کاهش کارایی.

- Write-Back (WBWA):

- تغییرات ابتدا فقط در کش ذخیره میشود و بعداً (هنگام تخلیه خط کش) به حافظه اصلی منتقل میشود.

- مزیت: نوشتن کمتر روی باس، کارایی بالاتر.

- عیب: خطر ناهماهنگی داده (Cache Coherency Problem).

مشکل همزمانی (Cache Coherency)

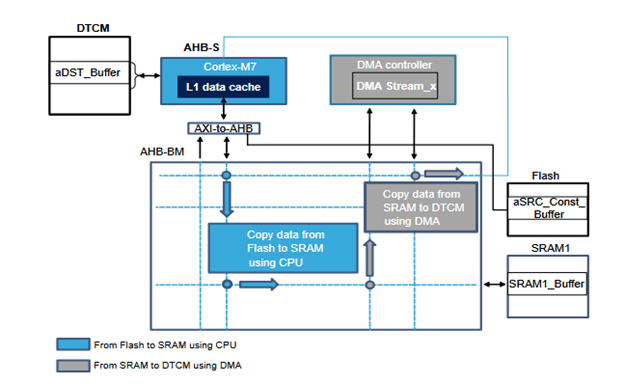

یکی از چالشهای بزرگ در استفاده از D-Cache زمانی است که چند Master به یک ناحیه حافظه دسترسی دارند. مثلاً:

- CPU داده را در SRAM1 تغییر میدهد ولی هنوز به حافظه اصلی ننوشته است.

- DMA همان داده را از SRAM1 میخواند و نسخه قدیمی را میبیند.

راهحلها:

- پاکسازی کش (Clean D-Cache): قبل از شروع DMA، کش را تخلیه کنیم تا دادهها به حافظه نوشته شوند.

- بیاعتبارسازی کش (Invalidate D-Cache): بعد از اتمام DMA، دادههای کش را حذف کنیم تا CPU نسخه بهروز را از حافظه بخواند.

- علامتگذاری ناحیه بهعنوان غیرقابل کش (MPU Config): برای حافظههای مشترک بین CPU و DMA.

- استفاده از Write-Through: برای این نواحی.

عملیاتهای نگهداری کش در STM32H7 (Cache Maintenance)

APIهای CMSIS برای کنترل کش در فایل core_cm7.h تعریف شدهاند:

- SCB_EnableICache() → فعالسازی I-Cache

- SCB_DisableICache() → غیرفعالسازی I-Cache

- SCB_EnableDCache() → فعالسازی D-Cache

- SCB_DisableDCache() → غیرفعالسازی D-Cache

- SCB_CleanDCache() → نوشتن دادههای تغییر یافته کش به حافظه

- SCB_InvalidateDCache() → بیاعتبارسازی دادههای کش

- SCB_CleanInvalidateDCache() → پاکسازی و بیاعتبارسازی همزمان

نکته: همیشه قبل از فعالسازی کش، آن را Invalidate کنید تا دادههای قدیمی مشکلساز نشوند.

جمعبندی

کش در STM32H7 ابزاری قدرتمند برای افزایش کارایی است، اما استفاده نادرست از آن میتواند مشکلاتی مثل ناهماهنگی داده ایجاد کند.

آشنایی با تفاوت I-Cache و D-Cache، سیاستهای نوشتن و تکنیکهای Cache Maintenance به شما کمک میکند پروژههایی سریع و پایدار پیادهسازی کنید.

در قسمت بعدی، یک مثال عملی از مدیریت کش را پیادهسازی خواهیم کرد تا ببینیم چطور میتوان بین کارایی بالا و حفظ همزمانی دادهها تعادل برقرار کرد.